## MASTER THESIS

# Federico Forti

# Efficient GPU Path Tracing in Solid Volumetric Media

Department of Software and Computer Science Education

Supervisor of the master thesis: Mgr. Oskar Elek, Ph.D.

Study programme: Computer Science

Study branch: Computer Graphics and Game Development

| I declare that I carried out this master the cited sources, literature and other professio I understand that my work relates to the No. 121/2000 Sb., the Copyright Act, as am Charles University has the right to concluthis work as a school work pursuant to Sec | rights and obligations under the Act lended, in particular the fact that the de a license agreement on the use of |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Act.                                                                                                                                                                                                                                                                | nature of the author                                                                                              |

Title: Efficient GPU Path Tracing in Solid Volumetric Media

Author: Federico Forti

Department: Department of Software and Computer Science Education

Supervisor: Mgr. Oskar Elek, Ph.D., Department of Software and Computer

Science Education

Abstract: Realistic Image synthesis, usually, requires long computations and the simulation of the light interacting with a virtual scene. One of the most computationally intensive simulation in this area is the visualization of solid participating media. This media can describe many different types of object with the same physical parameters (e.g. marble, air, fire, skin, wax ...). Simulating the light interacting with it requires the computation of many independent photons interactions inside the medium. However, those interactions can be computed in parallel, using the power of modern Graphic Processor Unit, or GPU, computing. This work present an overview over different methodologies, that can affect the performance of this type of simulations on the GPU. Different existing ideas are analyzed, compared and modified with the scope of speeding up the computation respect to the classic CPU implementation.

Keywords: GPU Volumetric Path Tracing, CUDA

I would like to thank Oskar Elek for supervising my thesis and all the people that have released volumetric data which makes this thesis possible. I would also like to thank all the people that have supported me during this time and the professors who showed me how to approach a research project.

# Contents

| In  | Introduction 3                                                                                                                                                                                                                                                                                                                                   |                                                                |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|

| 1   | Problem Statement  1 Radiative Transport Problem  2 Participating Media  3 The Volume Rendering Equation (VRE)  4 Porting to GPU  5 Limitations                                                                                                                                                                                                  | 5<br>5<br>6<br>7<br>8                                          |  |  |  |

| 2   | Related Work  2.1 Solving the Volumetric Rendering Equation                                                                                                                                                                                                                                                                                      | 9<br>9<br>10<br>10<br>11                                       |  |  |  |

| 3   | Background 3.1 Volumetric Path Tracing                                                                                                                                                                                                                                                                                                           | 13<br>13<br>18                                                 |  |  |  |

| 4   | Dptimization Methodology  1.1 Host Control or Device Control 4.1.1 Single Kernel versus Multi Kernel 4.1.2 Image Tiling 4.1.3 Summary  1.2 Maximizing Utilization and Hiding Multiprocessor Latency 4.2.1 Persistent Thread 4.2.2 Occupancy 4.2.3 Summary  1.3 Data Locality and Code Divergence 4.3.1 Compaction 4.3.2 Reordering 4.3.3 Summary | 24<br>24<br>27<br>28<br>28<br>29<br>31<br>32<br>33<br>36<br>38 |  |  |  |

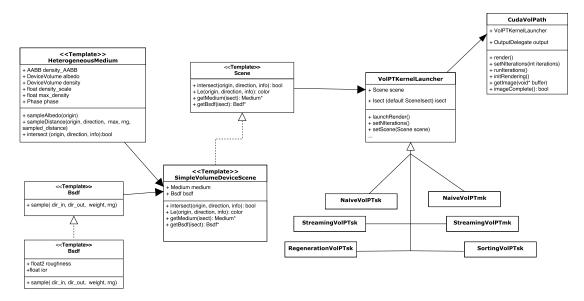

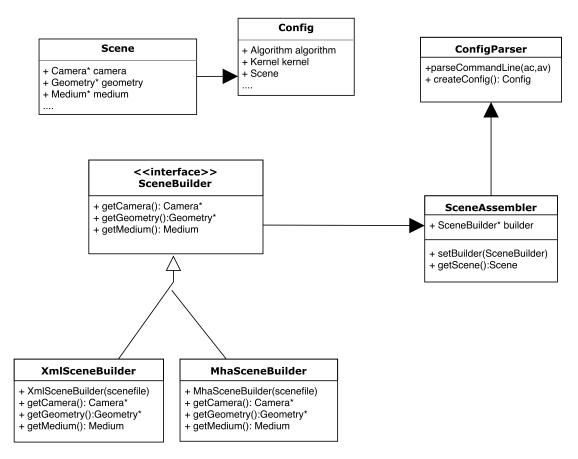

| 5   | mplementation Details 5.1 Generic Programming                                                                                                                                                                                                                                                                                                    | 41<br>41<br>41<br>42<br>44                                     |  |  |  |

| 6   | Results                                                                                                                                                                                                                                                                                                                                          | 46<br>48                                                       |  |  |  |

| ( ) | uclusion                                                                                                                                                                                                                                                                                                                                         | 49                                                             |  |  |  |

| Bibliography          | 50 |  |

|-----------------------|----|--|

| List of Figures       | 52 |  |

| List of Tables        | 54 |  |

| List of Abbreviations | 56 |  |

| Attachments           | 57 |  |

# Introduction

#### Motivation

In the last decade, graphics processor units have emerged as a cheap and powerful data parallel computational platforms. The architectural innovations, in such processors, have transformed the GPU from fixed-function hardware blocks to programmable units for general purpose computations (GPGPU). The gap between floating-point capability of GPU versus CPU is increasing on a year base and other hardware trends encourages to parallelize the existing serial algorithms (Nvidia [2017], McCool et al. [2012]). The evolution of new programming languages, like CUDA- Compute Unified Device Architecture- and OpenCL, gives to the programmer more flexibility in the usage of the GPU processors for general purpose computing. This processing power can be used today to address many of the computational problems, not solvable in adequate time with the previously available resources. The task we are going to focus on is realistic image synthesis of participating media. Most of the light effects, visible in nature, can be described by this type of media. Indeed, those are usually used to describe the property of a generic material. Realistic rendering of those materials requires physical simulations of the light interacting with the media. Those interactions can be thousands or millions based on the type of participating media we are going to simulate. For this reason, simulation of the light can take a long time. Efficiently, using GPU to compute in parallel, those light interactions can improve the time performance to get the final render.

# Possible Applications

Realistic image synthesis of solid object interests a wide range of areas. In architecture and product visualization can be used to present a building or a product. In virtual prototyping can be used to predict the appearance of an object before creating it and modifying it in according to that. Realistic Real time rendering is used inside many of the most famous games. Another possible application comes from volume visualization, where realistic rendering plays a central role in 3D shape perception. Most of the available implementation, in this sense, focuses more on performance, rather than perfect light transport simulation. The original idea for this project comes from the 3D printing field. In a recent paper Elek et al. [2017] have used volumetric rendering for accurate prediction of texture colors in 3D printing. This prediction stage is the biggest performance bottleneck of all the pipeline. The reason is that print materials have usually high optical density and simulating the appearance of those materials requires computing thousands of scattering interactions. This work aims to give a comprehensive view on how to optimize a volumetric path tracing for the GPU architecture, taking in consideration the advantages and disadvantages of different design choices. The solutions found can be used inside a completely GPU based renderer or as a stage of longer pipeline for rendering.

## Thesis Structure

The thesis has six chapters:

- the first chapter describes the problem that the thesis aims to solve.

- The second chapter shows the work that has already been done on solving this problem.

- The third chapter describe the theoretical background necessary for the methods that the thesis implements.

- The fourth chapter shows the method implemented and the different behavior of each method.

- The fifth chapter describes some implementation details on the solution adopted and the software created.

- Finally, the sixth chapter shows some results obtained with the GPU methods implemented and a comparison with a standard CPU algorithm.

# 1. Problem Statement

The chapter describes the problem that the thesis aims to solve and describe more in detail the different characteristics of Participating Media.

# 1.1 Radiative Transport Problem

The problem that the thesis aims to solve is a radiative transport problem and the radiometric quantity, that we are searching for, is the radiance L. This quantity describes how much light arrives from a direction  $\omega$  on an hypothetical differential area perpendicular to that direction  $dA^{\perp}$  Jarosz [2008].

$$L = \frac{d^2\Phi}{d\omega \ dA^{\perp}} = \frac{d^2\Phi}{d\omega \ dA \cos \theta}$$

(1.1)

Where  $\Phi$ , expressed in Watt (Joule/sec), is the radiant flux, i.e time rate of flow of radiant energy. When this light energy interact with a participating medium, than it can scatter or be absorbed. In both cases the light energy is attenuated. This attenuation is usually called extinction (see van de Hulst [1981]).

Extintion

$$=$$

scattering  $+$  absorption

In this type of problems a distinction is done between solid objects, which have a well defined boundary, and other media, like gases or liquids. In this work, we are concentrating on the first type of media, considering also cases where the object boundary defines a change on the index of refraction of the medium.

# 1.2 Participating Media

We can think of a participating media as an agglomerates of small particles. Each of those particles can be described by the following characteristics identified by van de Hulst [1981]:

- $C_{sca}$  (scattering cross section): is the area of the particle which is scattering light:

- $C_{abs}$  (absorption cross section): is the area of the particle that is absorbing light:

- F (scattering diagram of the particle): describes the scattering behavior and it can be used to obtain the more easily manipulable phase function  $f_p$ .

Given those characteristics, the final medium is described by the density function  $\rho(x)$  of these particles for any point x inside the medium. When a photon arrives to a point x, inside a medium which contains some particles, four types of event can happen:

**Absorption**: light is absorbed by the particles in that point x, proportionally to their  $C_{abs}$ ; the amount of light absorbed is defined as the absorption coefficient  $\sigma_a(x)[m^{-1}]$ .

$$\sigma_a(x) = C_{abs} \cdot \rho(x) \tag{1.2}$$

Out-scattering and In-scattering: light can be out-scattered or in-scattered in the point x, based on the  $C_{scat}$  of the particles in that point; the amount of light scattered is defined as the scattering coefficient  $\sigma_s(x)[m^{-1}]$ .

$$\sigma_s(x) = C_{scat} \cdot \rho(x) \tag{1.3}$$

**Emission**: finally the medium can emit more energy in the point x; we will call the radiance emitted by the medium in a point x and direction  $\omega$ ,  $L_e(x,\omega)$ .

There are also some derived quantities important to describe interactions with a participating media. Those are the extinction coefficient  $\sigma_t$ , defined as

$$\sigma_t(x) = \sigma_a(x) + \sigma_s(x) \tag{1.4}$$

and the albedo of the medium  $\alpha$ , defined as

$$\alpha = \frac{\sigma_s}{\sigma_t}. (1.5)$$

It is important to notice that it is always possible to derive the first two quantities in equations 1.2 and 1.3 from the last two equations 1.4 and 1.5, and vice versa. By integrating the extinction coefficient along a line segment l, we get the optical thickness of our material  $\tau$ :

$$\tau(l) = \int_{l} \sigma_t(x) dx. \tag{1.6}$$

Now, we have all the elements to completely describe the change of radiance inside a medium using the radiative transport equation (RTE), which can be defined with the following equation:

$$(\omega \cdot \nabla)L(x,\omega) = L_e(x,\omega) + \sigma_s(x)L_i(x,\omega) - \sigma_a(x)L(x,\omega) - \sigma_s(x)L(x,\omega). \quad (1.7)$$

where  $L_i(x,\omega)$  is the in-scattered radiance at x, through the direction  $\omega$ , coming by other scattered radiance. The equation 1.7 includes all the light interactions that we have previously described, which are in this order: emission, in-scattering, absorption, out-scattering.

# 1.3 The Volume Rendering Equation (VRE)

Scenes, containing solid participating media, are usually modeled as a volume  $\mathcal{V}$  and a boundary  $\partial \mathcal{V}$ , where  $\mathcal{V} \cap \partial \mathcal{V} = \emptyset$ . As shown by Matthias Raab and Keller, the transport can be described differently, based on the position considered on the volume. If the point is on the surface  $\delta \mathcal{V}$ , we use the classic Rendering Equation

$$L(x,\omega) = L_{e,\delta\mathcal{V}}(x,\omega) + \int_{S^2} f_s(\omega, x, \omega') L(x,\omega') |\cos\theta_x| d\sigma(\omega') : \qquad (1.8)$$

where  $S^2$  is the set of all directions (in this work we are using only the hemispherical formulation),  $f_s$  is the bidirectional scattering distribution function, which describes the scattering behavior at a point x on the surface (in particular is the fraction of incident differential radiation reflected into the direction  $\omega'$ ). Finally,  $\cos\theta_x$  is the cosine of the angle between direction  $\omega'$  and the surface normal at x (the reader interested on more informations about this equation can find its complete definition in the work of Kajiya [1986]). On the other hand, if the point is inside the participating media we have to consider the *Volumetric Rendering Equation* (VRE). This equation is obtained integrating the radiative transport equation, that we have described in the previous paragraph, along straight light rays until the next intersection point  $x_s$  of the ray with a surface. The equation is:

$$L(x,\omega) = \int_0^s T(x,x_t) \cdot L_v(x_t,\omega) dt + T(x,x_s) \cdot L(x_s,\omega)$$

(1.9)

where

$$L_v(x,\omega) = L_{e,\mathcal{V}}(x,\omega) + \sigma_s(x) \int_{S^2} f_p(\omega, x, \omega') L(x,\omega') d\sigma(\omega')$$

(1.10)

and  $T(x, x_t)$  is the transmittance function defined by the Beer-Lambert-Bougeuer law as

$$T(x, x_t) = e^{-\tau(||x - x_s||)}$$

(1.11)

with  $\tau$  the previously described optical thickness of the medium.

A more general equation, which combines both the equations 1.8 and 1.9, is the path integral formulation. In this formulation the space of integration is the union of spaces containing paths with specific length, i.e  $\mathcal{P} := \bigcup_{k \in \mathbb{N}} \mathcal{P}_k$ , where  $P_k$ is the space of paths  $\overline{x}$  of length k. The reader interested can find its derivation in the work of Veach [1997].

From a mathematical point of view, the volume rendering equation is a Fred-holm integral equation of the 2nd kind. Solving this type of equation analytically is very difficult, even applying simplifications on medium and light transport. Many numerical estimations methods have been studied in the literature. Those methods can be divided in two groups: deterministic methods and stochastic methods. The first ones are based on a discretization of the domain of integration and the solution of large linear systems. However, this type of system is usually affected by some limitations and the recent research has focused more on the second types of methods. In the next chapter, we are going to cover exactly this latter type of methods, giving an overview on some of the most important ones.

# 1.4 Porting to GPU

GPU-based programs have a number of limitations on when and how memory can be accessed. Computation speed increases at a much faster rate than memory access speeds, which means that, to improve time performance, special care should be taken to maximize bandwidth usage. Simulating light transport, inside participating media, can also be not obvious. For this scope, one of the most used

techniques in the industry of computer graphics is the Monte Carlo path tracing. This is a stochastic method which uses a random process to correctly estimate the light interactions in the medium. The random nature of this method makes the utilization of GPU difficult in this context. GPU is best suited to well predefined tasks with the minimum control decisions made at runtime. Random behavior of different GPU threads can lead to decreased utilization of the device. If a GPU is not utilized at its maximum processing power, the overhead of transferring data and control to it can make the GPU implementation slower than a CPU one.

#### 1.5 Limitations

This work is subject to different restrictions which limits the generality of the results obtained:

- we will not consider possible changes of refraction index inside the medium itself;

- our tested objects are rendered in the vacuum, not considering participating media outside the volume;

- inherited from the scattering theory used, we will consider only independent scattering, meaning that we will consider only participating medium which have well-defined separate particles, and single scattering, which means that the concentration of particles of the medium considered is proportional to the total light intensity scattered (further explanation inside the work of van de Hulst [1981]);

- we will not consider wave effects and only consider ray optics;

- we have tested our implementation only on one GPU architecture and we address only the usage of CUDA enabled GPU.

# 2. Related Work

In this section, we want to briefly overview some of the well established methods for rendering participating media solving the volumetric rendering equation 1.9 and the modifications proposed to port them on the GPU. After that, we will focus on one of those techniques and cover all the work that has been done on optimizing its implementation on GPU.

# 2.1 Solving the Volumetric Rendering Equation

We have seen in the previous chapter that our problem can be formulates as the solution of an integral, the volumetric rendering equation in 1.9. There are many possibility to estimate the value of this integral but all the algorithms, that we will treat here, are stochastic and *unbiased*, which means that the expected value of the stochastic estimator is equal to the value of the integral.

$$E[\langle I \rangle] = I$$

We are not going to cover in the next paragraphs the photon-mapping approaches, which are particularly good on rendering some difficult light effects, e.g reflected caustics. A GPU implementation of this type of algorithms can be found in the article by Davidovič et al. [2014]. The article describes GPU implementations of Progressive Photon Mapping, Stochastic Progressive Photon Mapping, Progressive Bidirectional Photon Mapping and Vertex Connection and Merging, which combine photon mapping approach to bidirectional path tracing, using multiple importance sampling. Moreover, a comparison between all the algorithm is presented which shows the advantage of using Path Tracing, for scenes which present no complex lighting.

# 2.1.1 Path Tracing (PT)

Path tracing (developed by Kajiya [1986]) is one of the most used algorithms in physically-based rendering and it is also the one that we decided to use for our GPU implementation. The reason being that GPU benefits from simple with high arithmetic intensity code. Path tracing is the most simple of all the presented algorithms even using participating media, which only requires distance sampling inside the media to extend the classic surface path tracer. Path tracing can also be coupled with next event estimation, a technique that allows direct connection of the paths with the light sources in the scene, by considering direct illumination from light sources and indirect illumination two separate Monte Carlo processes. This can really improve the converging time of the method in some scenes, for example when the light sources are very small. In this work, we decided to not include the next event estimations technique. In the context of GPU, using this technique means following different execution paths for threads that need to compute shadow rays and the others. Moreover, in the context of solid volumetric media this added contribution will be very small in most of the cases, because the contribution must be also attenuated by the transmittance function. Different authors have proposed efficient implementation of path tracing on GPU in the

context of surface rendering, we are going to cover those methods in the next section after discussing other alternatives.

#### 2.1.2 Bidirectional Path Tracing (BPT)

Bidirectional Path Tracing (developed by Veach [1997]) is a more sophisticated approach combining the advantages of path tracing with the dual method, which starts from the light source and light tracing, using multiple importance sampling for the final Monte Carlo estimator. In this technique, each approach is weighted and summed together and it can yield to unbiased estimations of the integral. The method can be easily generalized for participating media, but special care should be taken for the weights, which can be only approximated. Many authors have ported this algorithm to GPU without considering volumetric media. The first implementation was introduced by Novák et al. [2010], then van Antwerpen [2011] in a successive work improved it. The implementation increment the SIMD efficiency compared to a naive implementation. During a first phase of path generation, active threads are compacted together (we will add more details about this method in the chapter 4). During the connection phase, each GPU thread is used to evaluate every bidirectional connection. The method requires a higher memory consumption in comparison to the Path Tracing implementation. Moreover, in the work it is showed that even if the CPU implementation performs better than the classic Path Tracer, this is not the same for GPU, where the path tracer outperforms BPT in most of the scenes. In a successive work Davidovič et al. [2014] proposed Light Vertex Cache BPT; the key idea of this algorithm is that only a certain number of randomly chosen vertex are connected in the connection phase. This allows to store all the vertex in a single global cache of size given, by the average path length and to simplify the algorithm. The implementation offers a considerable speed up compared to the previous one and shows better performance than Path Tracing in scenes with complex lighting.

## 2.1.3 Metropolis Light Transport (MLT)

Metropolis Light Transport (MLT)Veach [1997] is a method which leverages Metropolis sampling to sample the path space. This allows to generate paths according to the type of function we are integrating (that, in our case, is the radiance coming from the rendered scene):

$$p(\overline{x}) = \frac{f(\overline{x})}{b}$$

where b is equal to the value that we want to estimate  $b = \int_{\mathcal{P}} f(\overline{y}d\sigma(\overline{y}))$ . The value of the latter can be estimated rendering the scene at low number of samples. One of the samples is then used as first state with a probability equal to  $\frac{f}{p}$ . The next states are then generated using the tentative transition function  $t(\overline{x} \to \overline{y})$ , which proposes a modification of the previous path. The modification is accepted or rejected based on the acceptance function. The method is highly affected by the proposal strategy and has also been explored in the participating media context. The implementation is based on identifying a path by the random number used to create it. The integral over the path space is then transformed to an integral

over the space of those numbers (the primary sample space). New paths in this method are created by perturbing the sample. However, both the algorithms have the risks to continue the computation over and over on the same area of the scene. To avoid that to happen, new random samples have to be generated after random intervals of time. Also this algorithm was addressed by Dietger van Antwerpen [2011]. In its implementation, the algorithm runs many MLT samplers in parallel and mutates the random numbers at the base of the method during the path generation phase. Moreover, the implementation builds on top of the BPT implementation previously described and inherits many of the improvements shown in that case. Also this method requires a high memory consumption respect to the Path Tracer implementation and the improvement achieved, using this technique, depends strongly on the type of scene. Furthermore, also in this case it is shown that, even if the CPU implementation performs better than Path Tracing, this is not true for what concerns GPU.

# 2.2 Efficient Implementations of Path Tracing on GPU

Path tracing is the core at the base of all the algorithms previously described. Consequently, an efficient implementation of this building block can have a positive effect also on the method previously described. We are not going to cover in this section the work done to reach high GPU performances ray casting large scenes. The reason being that our objective is to focus on a single volume, which requires only the intersection with a simple bounding box. The reader interested can look into the work done by Aila and Laine [2009], which describes the use of Spatial Bounding Volume Hierarchies (SBVH) on GPU. For the same reason we decided to not use any ray-shooting solutions, as NVIDIA's OptiX (more informations in the work of Parker et al. [2010]) or other frameworks, but rather to construct a new GPU solution from the ground up. In the introduction, we have talked about the challenges on porting a CPU algorithm to GPU. To build an efficient version of Path Tracing on GPU, it is essential to address full utilization of the available processing power. However, Path Tracing is a stochastic method, where each path traced can follow a different direction. The termination of some paths, before others, can reduce the full utilization of GPU. Nova'ak et al. Novák et al. [2010] have addressed this problem by regenerating terminated paths. This method uses persistent threadsGupta et al. [2012], which access a global pool of paths when the paths that are computed terminate. The method is improved by van Antwerpen [2011], who considered also compacting the active paths before regenerating new paths for the idle threads (see chapter?? for more explanation on this). A single kernel version of the described algorithm is given by Wald [2011], who proposed a tiled compaction rather than a global device compaction similar to the method we will show. However, the algorithm showed in the article does not give the expected results due to the hardware limitation in the number of registers available for a single kernel. Laine et al. [2013] propose a different type of path tracing which is best suited for scenes with complex materials requiring a lot of computation and thus leading to thread divergence. The methods use multiple lightweight kernels calls which allow to utilize all the resources present

on the GPU for the specific task. The paths are stored in a large pool of paths, which are sorted in chunks based on the specialized kernel they have to be used on. Davidovič et al. [2014] proposed a single kernel version of path tracing with regeneration, where regeneration is done singularly by each thread. However, in this implementation the regeneration is causing code divergence, which means that while the path is regenerating the other threads in the SIMD group (called warp in CUDA) have to wait before continuing. In this work, a different single kernel regeneration is used that prevents this divergence by regenerating the paths only when all the paths inside the warp have finished. Davidovič et al. [2014] provide also a performance comparison between the available algorithms with the result of having best comparable performances in the regeneration path tracer method with a single kernel and the streaming path tracer with multiple kernels. Frolov and Galaktionov [2016] proposed a different implementation of the path regeneration technique with the objective of lower self cost and avoiding moving ray data on different memory locations. They use tile-based work distribution and regenerate entire tiles instead of single threads only if the number of tiles to regenerate is greater than a certain threshold. Moreover, they apply thread compaction using shared memory for the threads associated to a tile...

# 3. Background

In this chapter, we will look more in depth at the background theory necessary to discuss this work.

# 3.1 Volumetric Path Tracing

We have seen in the previous chapter the volumetric rendering equation 1.9. Volumetric path tracing is a technique that tries to estimate this integral. For image synthesis we are usually interested on the radiance (in equation 1.1) which hits a virtual camera pointed toward our scene. In order to do that, it uses the Monte Carlo Integration framework, which we are briefly presenting in the next paragraph.

#### Monte Carlo Methods

Monte Carlo integration is a general tool for estimating integrals by randomly sampling the domain of integration given a probability distribution function p(x). More formally, this proposition, which we are not going to demonstrate, defines the Monte Carlo estimator.

Proposition 1. Given  $f: \mathbb{R}^d \to \mathbb{R}$  a function s.t.

$$I = \int_{\mathcal{Q}} |f(x)| \, dx < \infty$$

where  $Q \subset \mathbb{R}^d$  is a limited set. Let n random d-dimensional independent vectors  $X_1, \ldots, X_n$  with the same Probability Distribution Function (here and after PDF),  $p = p_{X_1} = \ldots p_{X_n}$ . We define the random variable:

$$\langle I \rangle_n := \frac{1}{n} \sum_{i=1}^n \frac{f(X_i)}{p(X_i)} \chi_{\mathcal{Q}}(X_i)$$

(3.1)

which we call estimator of I. then:

$$E(\langle I \rangle_n) = I \tag{3.2}$$

for any n > 0.

The framework works particularly well for complex high-dimensional integrals and its implementation is very simple, which is perfect for GPU algorithms. Increasing the number of samples the estimator converges to the exact solution with a standard deviation which follows  $\sigma = \mathcal{O}(n^{-\frac{1}{2}})$ .

## Ray integral estimator

Considering our integral in equation 1.9 the Monte Carlo primary estimator for the radiance L in the point x in the direction  $\omega$  is:

$$< L(x,\omega)>_{1} = \frac{T(x,X_{1}) L_{v}(X_{1},\omega)}{p(X_{1})}$$

(3.3)

if we use uniform sampling of the variable  $X_1$  respect to distance along the ray which start at x and ends at  $x_s$ , representing in this case the domain  $\mathcal{Q}$  of our integral, we have that

$$p(X) = \frac{1}{||x - x_s||}$$

and the estimator will be

$$< L(x,\omega)>_1 = T(x,X_1) L_v(X_1,\omega) ||x-x_s||$$

(3.4)

However, this simple estimator can lead to high variance when the medium is particularly dense. To improve the estimator, we can use a different PDF which simplifies the estimator. This technique is called importance sampling and in the next paragraph we will see how to sample based on the transmittance such that, rewriting the transmittance in terms of the distance along the ray  $s' = ||x - X_1||$  and considering the transmittance independent from x, we have

$$p(s') = \sigma_t(s') T(s') = \sigma_t(s') e^{-\int_0^{s'} \sigma_t(p)dp}$$

(3.5)

where  $\sigma_t(s')$  is a normalization term necessary to transform T(s') in a PDF.

#### Sampling distances according to the Transmittance

Woodcock tracking, which can be found in algorithm 1, is a technique allowing to sample a point along a ray so that the distribution follows the transmittance function. The algorithm needs the maximum extinction coefficient  $\sigma_{max}$  inside the medium. This coefficient is used to sample the distance according to the Beer-Lambert-Law. After that, the sample is rejected or accepted according to the real extinction coefficient  $\sigma_t(x)$  of the medium. If it is rejected, another step is taken according to the same law, otherwise the sampled distance is returned.

We are not demonstrating here the validity of this method to sample the distribution  $p(S) = \sigma_t(S)T(S)$ . For the interested reader we suggest the original article about the method by Woodcock and T.C. [1965].

## Directional integral estimator

Now we can sample from the probability distribution function defined in 3.5. The primary estimator for the integral inside the VRE in equation 1.9 in terms of distance along the ray  $s' = ||x - X_1||$  becomes

$$\langle L(x,\omega) \rangle_{1} = \frac{T(x, x + s'\omega) L_{v}(x + s'\omega, \omega)}{p(s')}$$

$$= \frac{L_{v}(x + s'\omega, \omega)}{\sigma_{t}(x + s'\omega)}$$

(3.6)

However, the term  $L_v$ , which can be found in equation 1.10, is constituted by another integral on the set of directions  $S^2$ , which means that after sampling a distance we have now to sample also a direction  $\omega'$ . Also in this case we could just sample according to an uniform distribution, but this will lead most of the times to an high variance estimator. A much better idea is to sample according to

**Algorithm 1:** Woodcock tracking: technique to sample the distance along a ray traversing an heterogeneous medium according to its transmittance function. This function is used for importance sampling the integral in the Volumetric Rendering Equation ( equation 1.9).

```

function woodcockTracking(\mathbf{x}, \omega, \sigma_{max}, s_{max})

Input: x: position on the ray,

\omega: direction of the ray,

\sigma_{max}: maximum extinction coefficient,

s_{max}: maximum distance of the ray,

rand() \in [0,1] random sample generator

Output: s': sampled distance along the ray

s' = 0;

while s' \leq s_{max} do

\begin{vmatrix} s' + = -\log_e(1 - rand())/\sigma_{max}; \\ \text{if } rand() < \sigma_t(\mathbf{x} - s'\omega)/\sigma_{max} \text{ then} \\ | \text{break}; \\ \text{end} \end{vmatrix}

end

return s'

```

some factor of the integrand, which is composed of the phase function  $f_p(\omega, x, \omega')$  and the radiance  $L(x, \omega')$ . The second term is more difficult to use as it is exactly what we are searching for, so in this work we will sample according to the phase function.

#### Henyey-Greenstein Function

In the first chapter, we have introduced the phase function as a characteristic of the medium we are going to render. In our work we are using as approximation of the Mie Phase functions the Henyey Greenstein function (abbreviated HG function hereinafter), the reader interested on other phase functions can read the comprehensive guide about multiple scattering by d'Eon [2016]. The Mie phase functions describe the scattering behavior of light interacting with perfectly spherical dielectric particles with different diameter size. The phase functions can be characterized by the anisotropy g, which is the first angular moment of the function:

$$g = \int_0^{2\pi} \int_0^{\pi} f_p(\theta', \phi') cos(\theta') sin(\theta') d\theta' d\phi'$$

(3.7)

where  $g \in [-1, 1]$  and, when it is positive, the light scatters predominantly into forward directions, while if it negative it scatters predominantly into backward directions. The HG function is parametrized by this value and can be written as:

$$f_{HG}(\theta, \phi, g) = \frac{1}{4\pi} \frac{1 - g^2}{(1 + g^2 - 2g\cos\theta)^{3/2}}$$

(3.8)

given this function a spherical direction  $(\theta, \phi)$  can be sampled inverting analytically the function (more information in the work of Pharr and Humphreys [2004])

$$\cos \theta = \frac{1}{|2g|} \left( 1 + g^2 - \left( \frac{1 - g^2}{1 - g + 2g\xi_1} \right)^2 \right)$$

(3.9)

$$\phi = 2\pi \xi_2 \tag{3.10}$$

where  $\xi_{1,2} \in [0,1]$  are uniformly distributed random samples.

#### Volumetric integral estimator

Now we can write the estimator for the term  $L_v$ , sampling the direction  $\omega'$ , with the technique described in the previous paragraph. We have that the primary estimator for the  $L_v$  term in the volumetric rendering equation 1.9 is

$$\langle L_{v}(x',\omega) \rangle_{1} = L_{e,v}(x',\omega') + \sigma_{s}(x') \frac{f_{p}(\omega,x,\omega')L(x',\omega')}{p(\omega')}$$

$$= L_{e,v}(x',\omega') + \sigma_{s}(x')L(x',\omega')$$

(3.11)

and combining all the results obtained, we have the final estimator

$$\langle L(x,\omega) \rangle_{1} = \frac{L_{e,\mathcal{V}}(x',\omega') + \sigma_{s}(x')L(x',\omega')}{\sigma_{t}(x')}$$

$$= \frac{L_{e,\mathcal{V}}(x',\omega')}{\sigma_{t}(x')} + \frac{\sigma_{s}(x')L(x',\omega')}{\sigma_{t}(x')}$$

(3.12)

where  $x' = x + s'\omega$ . In the work we are not considering medium which can emit light, we will have  $L_{e,\mathcal{V}}(x',\omega') = 0$  and the equation simplify to

$$\langle L(x,\omega) \rangle_1 = \frac{\sigma_s(x')L(x',\omega')}{\sigma_t(x')}$$

$$= \alpha(x')L(x',\omega')$$

(3.13)

where  $\alpha(x')$  is the albedo defined in 1.5. This estimator is very simple and perfect for GPU implementation, where the albedo can be easily mapped to an interpolated 3D texture. Using only one sample is usually not enough and, in its general description, the final estimator using n samples is

$$< L(x,\omega)>_{n} = \frac{1}{n} \sum_{i=1}^{n} \alpha(x') L(x',\omega')$$

(3.14)

## Volumetric Path Tracer Algorithm

The volumetric path tracer uses exactly this estimator on every pixel of the image sensor. In algorithm 3 a simplified version is presented only considering background light. The algorithm uses also the sampling from a Bsdf (Bidirectional scattering distribution function), that we have not described in the previous paragraphs (the reader can find its description in the work of Pharr and Humphreys [2004]). In this work a physically-based Bsdf is used, called the GGX. Whenever the point is a surface, the GGX is sampled instead of the phase function. We sample the GGX using the distribution of the visible normal. In particular, we are using the sampling strategy described by Heitz [2017] which does not require any look up table to be computed.

# **Algorithm 2:** Recursive estimator of L in the case we are only using background lighting

```

function radiance (x, \omega)

Input : x : position of the camera ray,

\omega: direction of the camera ray,

intersect(x,\omega) \to hit, s_{max}: intersection function for the scene,

returns weather the scene was hit and the distance s_m ax

\sigma_{max}: maximum extinction coefficient in the scene

Output: Radiance in the point and direction (x, \omega)

throughput = Color(1);

while (true) do

hit, s_{max} = intersect(x, \omega);

if (hit) then

s = woodcockTracking(\mathbf{x}, \omega, \sigma_{max}, s_{max});

if (s \leq s_{max}) and insideVolume(x) then

x = x + \omega s;

\omega = \text{samplePhase}(\omega);

throughput = throughput \cdot albedo(x);

else

x = x + \omega \, s_{max} \; ;

\omega, weight = sampleBsdf(\omega);

throughput = throughput \cdot weight;

end

else

return L_e(x,\omega) throughput;

end

end

```

#### Algorithm 3: Volumetric Path tracing algorithm

```

function volPT

Input: n iterations for the Monte Carlo estimator

Output: Rendered Image

Image = Image(0);

for pixel p in Image do

for n iterations do

x, \omega = \operatorname{cameraRay}(p);

p += \operatorname{radiance}(x, \omega);

end

p = p/n;

```

#### Russian Roulette

Another technique usually implemented with path tracing is the Russian Roulette. This technique permits to stochastically interrupt a path before reaching a light source. The probability of interrupting can be associated with the amount of light transported by the path. In this way is possible to interrupt with more probability paths which gives smaller contribution to the overall result. This technique is also unbiased if we modify our estimator by dividing for the survival probability of the path. More information about this technique can be found in the work by Pharr and Humphreys [2004]. In the software provided it is possible use the Russian Roulette inside any of the volumetric path tracer showed. However, we didn't focus the research on this particular aspect.

#### 3.2 GPU Architecture

In this section, we want to review some basics of the GPU architecture, that we are going to consider as a data parallel computational platform, and the characteristics of the CUDA platform.

#### Design Philosophy and Heterogeneous Programming

One of the most used classifications for computer architecture is the Flynn's Taxonomy. In this classification, the architectures are divided into 4 groups:

- Single Instruction Single Data (SISD): this is the traditional serial architecture.

- Single Instruction Multiple Data (SIMD): multiple cores execute the same instruction at the same time.

- Multiple Instruction Single Data (MISD): multiple cores use separate instructions on the same data.

- Multiple Instruction Multiple Data (MIMD) : multiple cores operate on multiple data streams.

Another type of classification can be done based on the memory:

- Multi-node with distributed memory: processors are connected by a network, each having its own local memory.

- Multiprocessor with shared memory: processors are either connected to the same memory or through a low-latency link, e.g. PCI-Express or PCIe.

Finally, we will use other two properties to characterize an architecture:

- throughput (ops/cycle or Tflop/s): rate of operations complete per cycle, usually calculated considering floating point operations and seconds (it can be sometimes confused with latency, cycle or s, which is the waiting time).

- bandwidth (GB/s): rate at which data can be transferred.

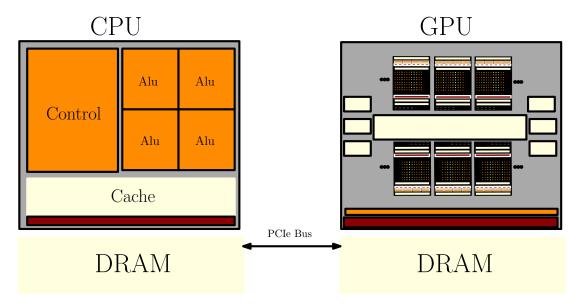

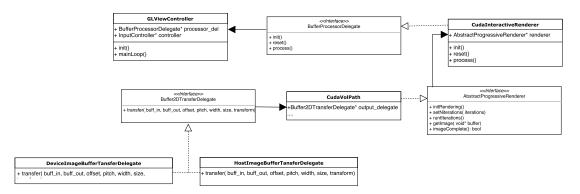

Figure 3.1: CPU and GPU, heterogeneous programming

In this context, GPU is a multiprocessor with shared memory architecture that utilizes SIMD groups, called warps. However, some of the features of the other architectures are also present on NVIDIA GPUs. NVIDIA call their architecture as Single Instruction, Multiple Thread (SIMT). At the base of the different performance between CPU and GPU is the different design philosophy of the architecture. Contrary to CPU, GPU are designed for high throughput and low latency tasks. GPU is many-core architecture which contain a high number of cores and high memory bandwidth. Each core is also very different from a CPU core. CPU cores are heavy-weight and they are designed to handle complex control logic, instead the GPU cores are very light-weight and optimized for data-parallel tasks with simple logic. For this reason, both architectures should be used together in a heterogeneous system for different scopes. Currently GPU cannot be used standalone and execution should be initialized by CPU. Therefore, the CPU is usually called the host and the GPU the device. In General Purpose GPU programming (GPGPU) execution of code on the device can be divided in different parts, which we will call kernels. The host code can call those kernels during its execution and execute the code of the kernel on the device side. The calls of those device kernels can also be asynchronous, allowing to the host to perform more work while the device is running the kernel.

## CUDA - Compute Unified Device Architecture

CUDA is a GPGPU platform introduced by NVIDIA for their GPU on 2006. It is designed for scalable parallelism allowing to any CUDA application to leverage whichever NVIDIA GPU they are running on. This is enabled by the usage of three main abstractions:

- hierarchy of thread groups

- memory hierarchy

- barrier synchronization

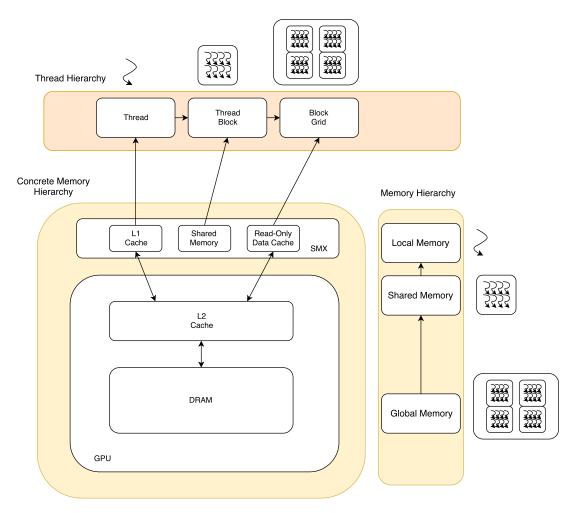

Figure 3.2: Memory and Thread Hierarchy. All threads can also directly access the read-only memory using the constant and texture memory. The concrete Memory hierarchy showed is relative to the Kepler Architecture (compute capability 3.0)

These abstractions are then mapped to concrete implementation on the specific hardware by CUDA. Figure 3.2 shows the thread and memory hierarchy and how the memory hierarchy is mapped to the Kepler GPU architecture. The programmer, to leverage all the parallelism of a GPU, must partition the multi-threaded program into blocks of threads which execute independently and in any order.

In the concrete, implementation of the CUDA model the GPU uses an array of Streaming Multiprocessors (SM or SMX). The multiprocessors schedule threads using SIMD groups of 32 threads called warps. However, threads in a warp can have their own instructions and they are able to branch and execute independently (also if this will not exploit the SIMD capability of the group potentially serializing the program). After the Kernel launch, a multiprocessor can get a thread block to execute. At this point, the warp scheduler partitions it into warps with consecutive thread ID. Program counters and registers of each warps are maintained on the multiprocessor for the entire life of the warp. For this reason, the multiprocessor can switch between different warps with no cost. The warp scheduler can also choose a warp, which active threads are ready to execute

their next instruction, while another warp is waiting (this is called in CUDA latency hiding). The number of block and warps and consecutively threads, that can be processed inside a multiprocessor, depends on the number of registers and shared memory used in the kernel, compared to the resources available on the multiprocessor. We will see what this means for the performance in 4. We want also to point out, in this section, that a CUDA application does not have to be bounded to the data which resides only on the GPU. The unified memory system gives the possibility to have a single address space between CPU and GPU memory (on newer SM architectures this means also on-demand page migration). Moreover, CUDA's zero-copy memory permits pinned memory location on the CPU to be accessed on the GPU. This last feature is used inside our application to give the possibility to load volume 3D textures, which are larger than the Device Global memory. Another feature of CUDA is the possibility to perform atomic operations. Those operations allow concurrent threads to perform read and write operations on data shared in global memory. However, this type of operation should be used carefully because it can potentially serialize the program in case all the threads wants to access the same data. For what it concerns shared memory, the system works differently. To achieve high bandwidth, shared memory is divided into several memory modules of the same size. Those modules are able to serve different read and write requests simultaneously, as long as the address requested resides in different banks. When two or more requested addresses reside on the same bank it is called a bank conflict and the accesses are serialized. However, there is an exception when multiple threads access the same 32-bit world, in that case the word is broadcast to all the threads requesting it (if multiple threads request to write, only one will write on the address, but which one is undefined). The banks are organized such that consecutive 32-bit words map to successive banks allowing to linear access to not cause bank conflict.

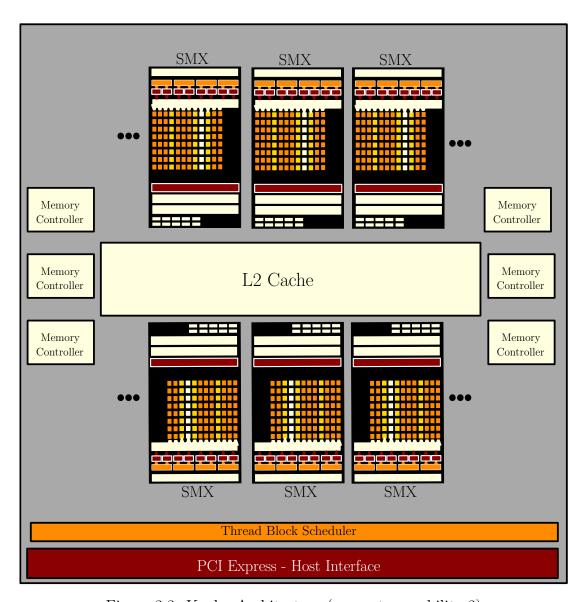

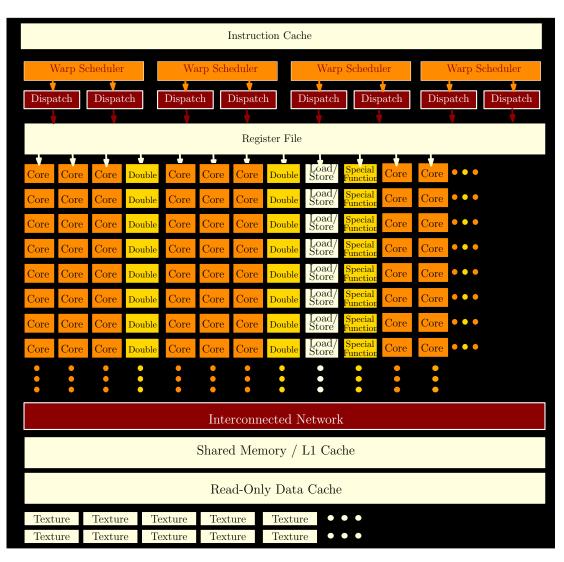

### Kepler Architecture

In this section we will detail the Kepler architecture (which is categorized by NVIDIA with compute capability 3). As shown in figure 3.3 and 3.4 in this architecture a multiprocessor consist of 192 CUDA cores for arithmetic operations, 64 double-precision units, 32 special function units, 32 load/store units allowing source and destination addresses to be calculated for sixteen threads per clock and 4 warp schedulers. Moreover, two types of cached memory are present: a L2 cache shared by all the processors, used to cache global and local memory accesses, and a L1 cache, used to cache access to local memory (including register spills). The same memory is also used for the shared memory. Each multiprocessor has also a read-only data cache which is used for constant or texture cache. The memory transactions are of the size of 128-byte for memory stored both in L1 and L2 cache and 32-byte if the memory is only cached in L2.

Figure 3.3: Kepler Architecture (compute capability 3)

Figure 3.4: Streaming Multiprocessor (Kepler architecture compute capability 3)

# 4. Optimization Methodology

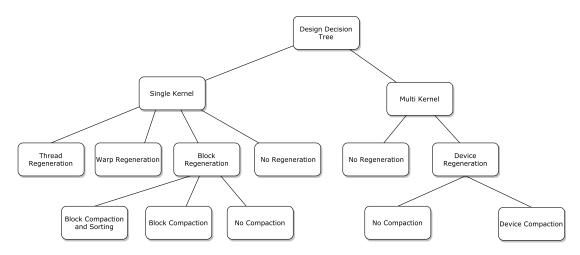

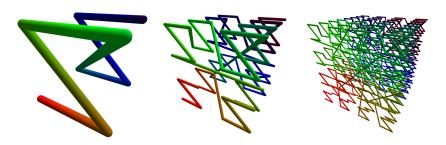

In this section we are going to present an overview of the method used to optimize the volumetric path tracer. The chapter follows the design decisions that someone should evaluate when approaching this type of problem. Different design paths have different advantages and disadvantages that we are going to cover. In figure 4.1 it is possible to see the exact design decisions tree. At the beginning, we are going to examine how to use GPU and CPU together and this we lead us to a decision on a single versus multi kernel approach. After that, we are going to evaluate how to maximize the utilization of GPU regenerating threads, which become idles during the computation. Finally, we are going to see how to maximize the memory throughput and the data locality compacting together the threads that are still active. In figure 4.2 there are some scenes that we are going to use for the tests: two of them from the application field of 3D printing and the other two from visualization. The volumetric path tracer tests showed in this section are all running without Russian Roulette 3.1.

## Testing Hardware

We will use for testing a MacBook Pro with CPU Intel Core i7 quad-core and GPU Nvidia GeForce 650M with the following characteristics:

- Kepler architecture, compute capability 3.0

- Total amount of global memory: 512 MB

- Total number of registers available per block: 65536 (equal to registers per SM)

- Maximum number of threads per block: 1024

- Total amount of shared memory per block: 49152 bytes

more details about the hardware are provided in the Appendix.

#### 4.1 Host Control or Device Control

#### 4.1.1 Single Kernel versus Multi Kernel

The topic of using a single "megakernel" versus multiple lighter kernels has already been widely covered in the literature. A naive single kernel implementation holds all the algorithm and requires all the resources associated with all the different parts of it. Nvidia OptiX (Parker et al. [2010]) utilizes a similar but more sophisticated approach. In this framework, a Just-In-Time compiler combines all the different stages of the path tracer, in the form of PTX (assembly language for NVIDIA GPU), into a single kernel. The kernel is formed as a state machine where, to minimize execution divergence, a scheduler selects a single state for an entire SIMT unit. If a thread is not requiring that state, it remains idle during that iteration. Laine et al. [2013] compared the traditional single kernel approach

Figure 4.1: Design decision tree. This tree represent the design decisions made to optimize a GPU path tracer. In the first level, the first decision is regarding the use of a single or a multi kernel and more in general, giving more control to the device or to the host. The second level contains all the possibility presented to optimize the utilization of the GPU. Finally, the last level contains the possibility to decrease data access latencies in a volumetric path tracer.

to a wavefront formulation, which uses different kernels for different control flows. This method allows to completely avoid code divergence, i.e. sorting the paths based on their next interaction, dividing them into different bins and launching a kernel only for the paths in the same bin. Moreover, the kernels launched are perfectly specialized for the task and they can utilize the GPU resources completely. However, this work is not containing this possibility. There are different reasons for that:

- Dynamic parallelism and global device synchronization: supported only by the newer CUDA GPU (compute capability 3.5 and higher), dynamic parallelism gives the ability to a single CUDA thread of launching a new kernels with its own configuration. This technique reduces the need to transfer execution control and data between host and device (Nvidia [2017]). Moreover, the global device synchronization introduced with CUDA 9.0 (using special cooperative groups) removes the need of launching a new kernel only for synchronizing all the threads running on the device.

- The type of scenes that we are analyzing in this work contains just one object: the volume that we want to render. For this reason there are not many different type of interactions. The only two cases are if the analyzed point is inside the volume or on the boundary (exactly how it is explained in the section 1.3). However, the wavefront formulation is best suited for scenes with many different and complex materials.

Inspired by results showed by others like Davidovič et al. [2014] and van Antwerpen [2011] the only multi kernel approaches that we are going to analyze are composed by a maximum of 2 kernels. The table 4.1 shows the difference on using a naive approach with a single kernel call or multiple kernel calls. The naiveSK method (naive with a single kernel) consists of a simple volumetric path tracer implementation where each thread computes only one path and all the

(a) ad scene: rendering of a slab with grid resolution (320,320,100). The texture "printed" on the surface has a depth equal to 10 (10% of the total resolution depth) and it is assigned to the albedo volume, the rest of the albedo volume is white. The density volume is always constant and equal to 100.

(b) cgg-logo scene: rendering of a solid unit cube with a grid resolution of (100,100,100). The texture "printed" on the surface has a depth equal to 10 (10% of the total resolution depth) and it is assigned to the albedo volume, the rest of the albedo volume is white. The density volume is always constant and equal to 100.

(c) artifix scene: rendering of the publicly available artifix Data set (Osirix) which have grid resolution of (128, 87, 128). The data has been used to create the density volume, the albedo has been created from the density using a transfer function which maps the density from gray to red to blue based on the density value. The maximum density value is 100.

(d) manix scene: rendering of the publicly available Manix Data set (Osirix) which have grid resolution of (128, 115, 128). The data has been used to create the density volume, the albedo has been created from the density using a transfer function which maps the density from gray to red to blue based on the density value. The maximum density value is 100.

Figure 4.2: Test scenes. top: scenes for 3D printing application, bottom: scenes for data visualization.

Table 4.1: Single Kernel versus Multi Kernel (naive). The speed of the methods is analyzed in terms of millions of traced rays per second (rays/sec). The test has been done using the scene in figure 4.2b rendering a 400x400 image for 100 iterations (number of samples for the Monte Carlo estimation)

| Method  | rays/sec |

|---------|----------|

| naiveSK | 3.91     |

| naiveMK | 1.19     |

data is stored on local memory (the algorithm can be found in the work of Davidovič et al. [2014]). The naiveMK method (naive with multiple kernels) consists of a simple volumetric path tracer divided in two kernels. The first kernel is generating the paths and computing the first intersection with the object, while the second kernel extends the active paths computing a new intersection with the scene. It is clear that the single kernel approach wins over the multi kernel one in terms of speed. However, there are also advantages on using multiple kernel calls. From a user perspective, using smaller kernels allows the CPU to take the control of the application and, in case only one GPU is available in the system, it avoids to freeze the user interface for too much time.

#### 4.1.2 Image Tiling

Another possibility for interleaving the control between host and device is using image tiles. That is, the image is divided into equal tiles and the device can work on each of them separately at the same time. This technique allows to lower the memory requirements for running the software, because we need only to store the size of one tile. This also means that the rendering is divided into multiple kernel calls. Each of this kernels have to render a single tile and for this reason is faster. In this perspective, it is important to not use tiles that are too small, because this will decrease the utilization of the hardware and therefore the performance (we will talk more about utilization in the next section). The consequence is that, in order to obtain the maximum performance, the size of the tile should depend on the type of hardware. The tile size is also affecting the specific algorithm in use. Most of the algorithms that we are showing in this work have different memory requirement and different behaviors depending on the tile size. However, from our tests it emerges that the behavior of each algorithm using different tile sizes is comparable with the use of different number of samples. Potentially, a tiled image allows also to decrease the time to transfer the image from the device to the host. In the practical case, however, the size of the image is usually small and the time to transfer it is not comparable with the time for computation. For this reason, also using a second buffer for the image tile (this technique is usually called Double Buffering) and the CUDA asynchronous memory copy to overlap computation and image transfers, the performance improvement is negligible. Table 4.2 shows the results of using different image tiles. From this table it is possible to see that launching multiple kernels on different image tiles is not affecting the performance as far as the number of tiles is not becoming too high. Indeed, the computation remains stable until the number of pixel processed

by the algorithm becomes too small, decreasing the utilization of the device for the kernel call. This result shows also that the real performance bottleneck on dividing the path tracing task is not represented by the kernel launch overhead but from the repetitive loading and storing of the same data.

Table 4.2: Different image tiling settings used for rendering a 1920x1920 image with the scene in figure 4.2b. In the table the number of paths processed per tile is compared to the time to render the all image. Note that, opposed to the naiveSK, the streamingSK kernel launching configuration does not depend on the number of paths processed but rather on the threads available on the GPU. For this reason when the number of paths processed becomes low the naive method improve its performance while the streamingSK decrease in performance.

|                   | tiling setting |         |         |        |         |          |

|-------------------|----------------|---------|---------|--------|---------|----------|

|                   | (1,1)          | (2,2)   | (4,4)   | (8,8)  | (32,32) | (64, 64) |

| n. paths per tile | 18432000       | 4608000 | 1152000 | 288000 | 18000   | 4500     |

| StreamingSK       | 61.27          | 67.98   | 72.72   | 76.13  | 90.66   | 224.04   |

| regeneration SK   | 7.99           | 10.02   | 9.44    | 9.48   | 34.11   | 98.40    |

| naiveSK           | 219.47         | 223.65  | 221.93  | 224.59 | 224.85  | 123.32   |

#### **4.1.3** Summary

In this chapter we have seen the first design decision that should be made when approaching this problem: giving the control of the program to the host or to the device. In the first case, the advantage is to have a more responsive UI and, if the kernels are well divided into different tasks, it allows to use efficiently the device resources for the task. In our case, most of the computation concerns the same simple task: the interaction with the medium. For this reason, dividing the computation will not improve the performance. We have also seen another way to divide the computation by rendering separate image tiles. This allows to use the same algorithms on a different hardware, whose memory requirements depend on the image tile size. Moreover, overlapping communication and computation decreases the latency on getting the resulting image. The tile size is affecting also the utilization of the GPU which is upper bounded by the number of paths to compute. Indeed, the number of paths to compute an image tile is equal to

paths = tile.width  $\cdot$  tile.height  $\cdot$  iterations.

While the number of iterations is given by the user, the tile width and height can be specified according to the hardware used, which allows to improve the utilization for the specific hardware. In the next chapter we will see which other factors can decrease the utilization of the GPU and how to prevent it.

# 4.2 Maximizing Utilization and Hiding Multiprocessor Latency

The objective of maximizing the utilization of the device is achieved when the device is always active until the end of the computation. In a path tracer, the

problem is given by the different lengths of the paths computed. When a path in a thread has terminated, that thread will not be utilized until the termination of all the others. To overcome this inefficiency Novák et al. [2010] have proposed to use path regeneration. This technique consists of using a persistent thread system (more information about persistent thread programming can be found in the work of Gupta et al. [2012]) where new paths, taken from a global pool of paths, are assigned to idle threads (the path is therefore regenerated).

Another problem that can affect the utilization on the system is the number of registers and the shared memory necessary for the kernel. Most of the time those resources are stored in a fast memory (L1 cache in devices with compute capability 3 or higher) that is limited. When the kernel reaches this limit the maximum number of resident blocks in a multiprocessor is decreased. If the kernel requires more registers than available on the multiprocessor, then the compiler will attempt to minimize register usage, or it can be forced to do it, while keeping them stored in the local memory (register spilling). On the other hand, if the kernel requires too much shared memory the only solution is to decrease the number of resident block in a multiprocessor. When the number of threads resident on the same multiprocessor is high then the latency of a inactive warps, which cannot perform their next instruction, can be hidden efficiently. The full utilization in this case is achieved when the warp scheduler can always issue some instruction for some warp during the latency period.

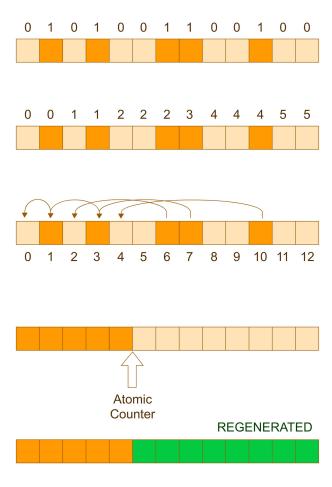

#### 4.2.1 Persistent Thread

The persistent thread style of programming helps a developer to separate the task to compute from the hardware that is running it. The threads are active for the entire duration of a kernel and every thread gets new work from a work queue when it finishes its current task. In our case this means regenerating the terminated paths and tracing new ones. A new path can be created by using an identification number like in algorithm 4. For this reason, the work queue is represented by one global value that is atomically incremented during regeneration. In this paragraph, we analyze the different approach that we may take for regenerations:

- Thread regeneration: a single kernel is launched and new paths are assigned to every thread. When the thread becomes inactive the path is regenerated.

- Warp regeneration: a single kernel is launched and new paths are assigned to every warp. When all the threads in a warp become inactive, all the warp is regenerated incrementing the atomic counter only once per warp by the size of the warp.

- Block regeneration: a single kernel is launched and new paths are assigned to every block. At every path extension, if the path queue is not empty, all the threads in a block are synchronized and all the inactive ones are regenerated.

- Device regeneration: multiple kernel are launched, one kernel is performing regeneration and another one path extension. If the path queue is not empty, after each extension all the inactive threads are regenerated.

Those regeneration techniques require different types of synchronization points: the first one is the classic implementation where if a thread becomes inactive it is immediately regenerated, i.e if only one thread is regenerating the rest of the threads in the warp, we have to wait for it before continuing. The second one is using the warp vote functions (which can be found in the documentation by Nvidia [2017]) to decide weather to regenerate or not the warp. In CUDA 9 and on devices with compute capability higher than 3.0 this can be efficiently done using the warp shuffle functions, which allows to exchange values between threads in the same warp, to get the right path for each thread. The third one requires synchronization of all the threads in a block and it regenerates all the block all together. This latter is similar to what is done by Frolov and Galaktionov [2016]. Finally, the last one is regenerating all the processed paths and requires to synchronize all the devices. We did not include this last one in our study because we have already tested that the multi-kernel approach is not favoring our settings. In the implementation presented the synchronization points are performed after each path extension (unless the path queue is empty). This can be not optimal, as the synchronization point for regeneration should be placed exactly when the performance risks to decrease for not having enough active threads (in the next paragraph we will see what exactly this means). However, this is not only hardware dependent but also scene dependent. For this reason, we did not include this variation in this work. The table in 4.6 shows the results of the different methods on our scenes. We can see that the regeneration SK (regeneration with a single kernel) on a single thread works best on the scenes with constant density (cgg-logo and ad) for which the warps are almost always synchronized. In the other two scenes the warp regeneration is performing better. When the paths start to differentiate, this method allows to maintain the coherence inside a warp by restarting all the warp at once.

Algorithm 4: pseudo-code of a function which regenerate a thread. The algorithm uses a global counter for the number of rays already traced. This counter is used to define the identification number of a ray which is also used to create the ray starting from the camera

Table 4.3: comparison of different types of regeneration on the scenes presented in figure 4.2. Three regeneration approach are taken in consideration: regenerationSK (thread) doesn't require any type of synchronization and regenerate a thread immediately after it becomes idle. regenerationSK (warp) require all the warp to be idle before regenerating. regenerationSK (block) is synchronizing all the block and regenerating only when all the block is idle. Finally, the naiveSK approach is a simple volumetric path tracer which is not performing any regeneration.

| method                  | rays/sec |       |         |       |

|-------------------------|----------|-------|---------|-------|

|                         | cgg-logo | ad    | artifix | manix |

| naiveSK                 | 3.88     | 2.13  | 8.34    | 8.45  |

| regenerationSK (thread) | 81.62    | 42.37 | 11.80   | 11.42 |

| regenerationSK (warp)   | 17.13    | 17.05 | 12.11   | 14.82 |

| regenerationSK (block)  | 3.52     | 3.21  | 7.35    | 7.41  |

#### 4.2.2 Occupancy

The occupancy of a kernel consists of the number of active warps (SIMD group) on a multiprocessor when launching the kernel. If the occupancy is maximal, then all the warps that can simultaneously reside on a multiprocessor are active and the warp scheduler can hide the latency of the warps which cannot execute their next instruction. However, if the kernel requires too many registers or too much shared memory, it have to limit the number of threads active on a single multiprocessor. If the kernel requires too much shared memory, there is nothing that the compiler could do to increase the occupancy. However, if the problem is the number of registers used, then one possibility is to limit this number using register spilling. In our case, the kernel of our volumetric path tracer requires approximately 64 registers for the compiler, which limits the occupancy to 50%. To achieve the 100% of occupancy we could force the compiler to reduce the number of registers used by our path tracer.

#### Bounding Register Usage

Bounding the number of registers used by a kernel is not always a good idea. The compiler is usually limiting the number of register used by itself and tries to make the best decision between increasing the occupancy and efficiently storing memory on registers. Sometimes, however, it is possible that this decision is not the one that gives the best performance. For this reason, another possibility is to force a kernel to use a minimum number of blocks per multiprocessor by limiting even more the number of registers used. In the table 4.4 we can see the effect of achieving maximum occupancy using this technique. All the results are worse respect to the version with half the occupancy in table 4.6. By analyzing the process, it is possible to see that also if the number of warps in the multiprocessor is maximum, the latency is higher than before. The time required to get the spilled registers is therefore higher than the latency hiding capability of the device.

Table 4.4: maximize occupancy decreasing registers usage. In those results the number of register used by the kernels is bounded so that the device can achieve maximum occupancy. However, comparing those results with the ones in table 4.6 is possible to see that this method is actually performing much worse than the previous one with only 50% of occupancy

| method                  | rays/sec |       |         |       |

|-------------------------|----------|-------|---------|-------|

|                         | cgg-logo | ad    | artifix | manix |

| regenerationSK (thread) | 39.04    | 32.81 | 12.66   | 11.37 |

| regenerationSK (warp)   | 4.37     | 7.02  | 11.92   | 10.95 |

#### Maximize Register Usage

Increasing the occupancy is not the only way to hide threads latency; another possibility is to leverage the instruction-level parallelism. Indeed, a warp that has subsequent independent instructions can hide the latency of an instruction performing the next one. This technique allows to lower the occupancy needed to obtain the device peak of performance, which can be calculated with Little's law:

$$parallelism = latency \cdot throughput$$

We have used this technique in our volumetric path tracer by assigning more than one path to each thread. This allows to decrease the dependency among subsequent instructions and, therefore, to hide the latency inside a single thread using the instruction-level parallelism. Recent tests Volkov [2015] have demonstrated how the use of more registers per thread, using less threads per multiprocessor, can lead to better performance with smaller occupancy. We have also tested our volumetric path tracing with a smaller occupancy, but without any visible improvements. The conclusion that we may take is that in this case the compiler is doing an optimal choice about the number of registers and threads to use.

### **4.2.3** Summary

We have seen in this section different application of the persistent thread techniques, which differ on synchronization points. Moreover, we have seen some techniques to achieve better performances at lower occupancy utilizing instruction-level parallelism and more registers per thread. However, the difference in latency between arithmetic operations and memory operations is high and the best way to improve the performance is decreasing this gap. For this reasons, in the next section, we will discuss about localizing memory access inside the kernels to maximize the cache usage and decrease the memory access latency.

## 4.3 Data Locality and Code Divergence

We have discussed until now all the performance limiting factors regarding the full utilization of the GPU and the logic communication between host and device. In this chapter, we are going to discuss about one of the most important limiting factor in GPGPU: the bandwidth. In the section 3.2 we have seen that access

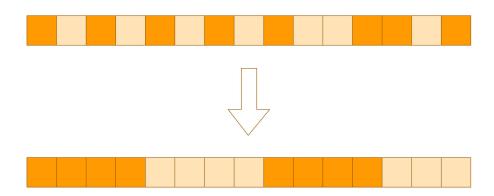

on every level of GPU memory hierarchy have different bandwidth. Localizing the data access inside a kernel is a key factor for decreasing the number of low bandwidth data transfers. Code divergence is another limiting factor which can drop the performance causing the instruction throughput to decrease. When a warp executing a kernel meets a flow control instruction, it diverges if the threads in the warp follow different flows of execution and if the different instructions are substantial (otherwise predication is used). The hardware maintains a bit vector of active threads and executes the code once for the active and then for the inactive. When all the executions paths are complete the warp re-converge to the original path. All those limitations are present in a Monte Carlo Path Tracer that is based on a random control flow and thus random memory access. It is not straightforward to create a predetermined data access pattern that can be exploited in this case. Dietger et al. van Antwerpen [2011] have proposed a solution based on stream compaction of the active threads at every path extension. In this solution, paths that are still active are compacted together and stored in the global memory of the device. In this section, we will propose a new method that aims to merge the benefits of compacting with the reordering of the rays to exploit warp and data coherence.

#### 4.3.1 Compaction

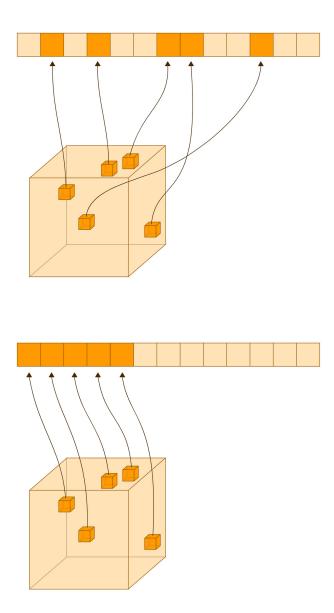

As we have already discussed in the introduction of the chapter, active thread compaction allows to separate the threads into active and idle. There are two main advantages on using this approach for a MC path tracer:

- 1. SIMD efficiency increase: the compaction of the active threads allows to have warps fully active or fully inactive.

- 2. Primary ray coherence is maintained: the regenerated paths usually follow the same control flow path during the first iteration without any code divergence and access the same GPU caches exploiting data locality.

Also in this case we want to analyze the different approaches to compaction:

- Device Compaction (StreamingMK): all the active threads inside the device are compacted together. The methods requires two streams of global memory for path data one in input and one in output. The compaction is efficiently performed using an atomic operation which tracks the number of elements written to the output stream. This method requires two kernels, one for regenerating inactive paths and one for extending the paths.

- Tiled Block Compaction (*StreamingSK*): the active threads are compacted only inside a block. The path data is still stored in the global memory, but the compaction of the active threads is performed only on a tile of this data, large as much as the number of threads inside a block. The graphical output of the compaction can be seen in figure 4.4 and pseudo-code in algorithm 5.

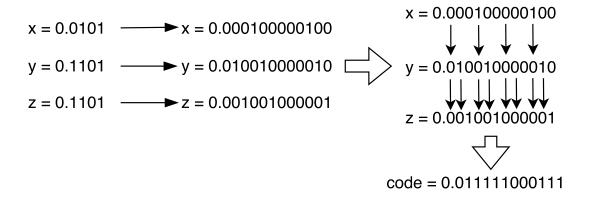

In both cases the compaction is performed by the following steps (which are graphically showed in figure 4.3):